近日,中国科学院大学教授周武课题组与合作单位共同研究,提出了一种全新的基于界面耦合的p型掺杂二维半导体方法,打破了硅基逻辑电路的底层“封印”,基于量子效应获得了三维(3D)垂直集成多层互补型晶体管电路,为后摩尔时代未来二维半导体器件的发展提供了思路。近日,该项由中国科学家主导的半导体领域新成果登上Nature。

经过数十年发展,半导体工艺制程已逐渐逼近亚纳米物理极限,传统硅基集成电路难以依靠进一步缩小晶体管面内尺寸来延续摩尔定律。发展垂直架构的多层互连CMOS逻辑电路以实现三维集成技术的突破,已成为国际半导体领域积极探寻的新方向。在2023年12月美国旧金山召开的国际电子器件会议(IEDM)中,三星、台积电等半导体公司争相发布相关研究计划。

由于硅基晶体管的现代工艺采用单晶硅表面离子注入的方式,难以实现在一层离子注入的单晶硅上方再次生长或转移单晶硅。虽然可以通过三维空间连接电极、芯粒等方式提高集成度,但是关键的晶体管始终被限制在集成电路最底层,无法获得厚度方向的自由度。新材料或颠覆性原理因此成为备受关注的重要突破点。

近日,中国科学院大学教授周武课题组与山西大学教授韩拯课题组、辽宁材料实验室副研究员王汉文课题组、中山大学教授候仰龙课题组、中国科学院金属研究所研究员李秀艳课题组等合作,提出了一种全新的基于界面耦合的p型掺杂二维半导体方法。

该方法采用界面效应的颠覆性路线,工艺简单、效果稳定,并且可以有效保持二维半导体本征的优异性能。

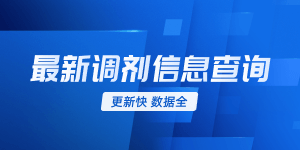

在此基础上,该研究团队利用垂直堆叠的方式制备了由14层范德华材料组成、包含4个晶体管的互补型逻辑门NAND以及SRAM等器件(如图1所示)。

这一创新方法打破了硅基逻辑电路的底层“封印”,基于量子效应获得了三维(3D)垂直集成多层互补型晶体管电路,为后摩尔时代未来二维半导体器件的发展提供了思路。

图1. 二维半导体垂直3D集成互补型逻辑电路SRAM原型器件的实现

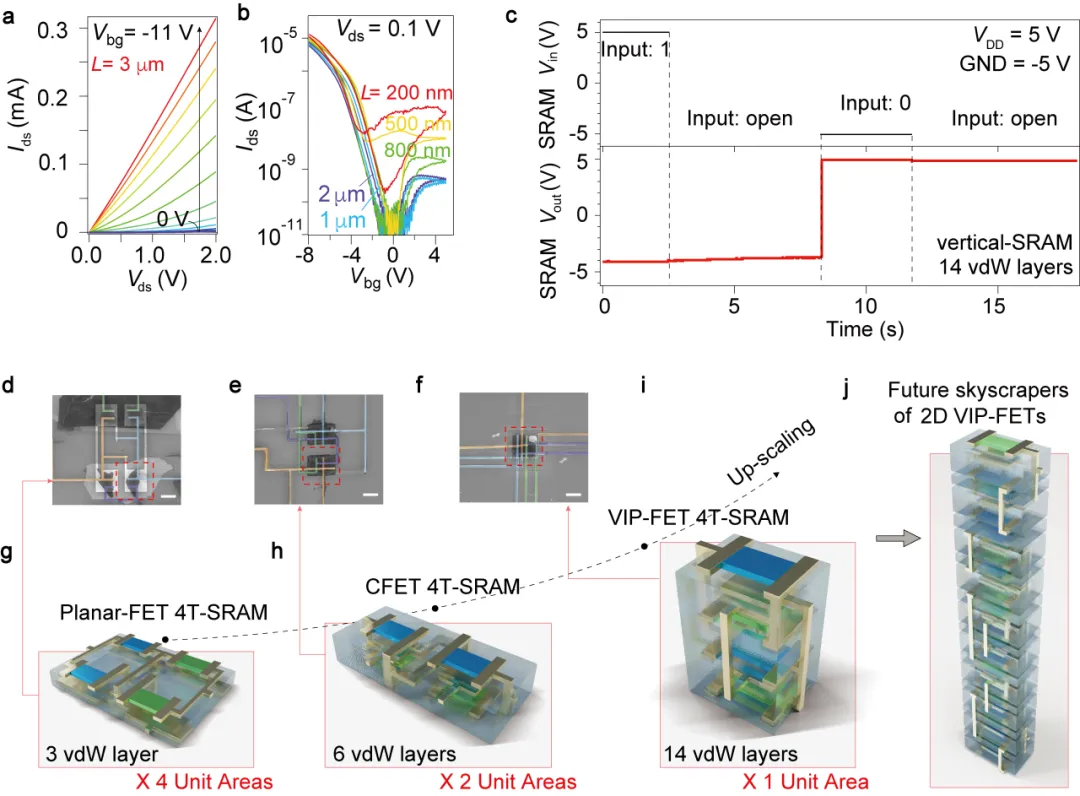

利用低电压球差校正扫描透射电镜,该研究团队对由14层范德华材料组成的NAND器件的截面结构进行了原子尺度的深入表征。

分析结果表明,器件关键组分MoS2、CrOCl与h-BN层之间具有原子级清晰的界面,相应的电子能量损失谱化学成像进一步证实了这一结论(如图2所示)。密度泛函理论计算揭示了这种界面耦合诱导的极性反转源于过渡金属硫族化物(TMD)材料向CrOCl的电荷转移以及伴随的电子间相互作用。

该掺杂策略预期可广泛适用于TMD材料与具有高功函数的层状绝缘体之间的界面,有望推动半导体电路先进三维集成的进一步发展。

图2. 包含14个范德华材料层的三维集成逻辑电路的原子尺度结构分析

近日,相关研究成果以“Van der Waals polarity-engineered 3D integration of 2D complementary logic”为题在线发表于Nature。中国科学院金属所研究生郭艺萌、博士后李江旭,山东大学教授詹学鹏,中国科学院大学研究生王春雯,上海科技大学研究生李敏为论文共同第一作者。李秀艳、侯仰龙、周武、王汉文、韩拯为论文共同通讯作者。北京大学教授王润声、研究生王子瑞在TCAD仿真方面给予支持,山西大学教授张靖、秦成兵在测试方面给予支持,北京大学教授叶堉提供CrOCl晶体和测试的协助,上海科技大学教授刘健鹏为DFT计算提供支撑。

该研究得到科技部纳米科技重点专项、国家自然科学基金、沈阳材料科学国家研究中心、辽宁材料实验室、山西大学量子光学与光量子器件国家重点实验室、北京高校卓越青年科学家计划项目、中国科学院稳定支持基础研究领域青年团队计划和中国科学院大学电子显微学实验室等的资助。

① 凡本站注明“稿件来源:中国教育在线”的所有文字、图片和音视频稿件,版权均属本网所有,任何媒体、网站或个人未经本网协议授权不得转载、链接、转贴或以其他方式复制发表。已经本站协议授权的媒体、网站,在下载使用时必须注明“稿件来源:中国教育在线”,违者本站将依法追究责任。

② 本站注明稿件来源为其他媒体的文/图等稿件均为转载稿,本站转载出于非商业性的教育和科研之目的,并不意味着赞同其观点或证实其内容的真实性。如转载稿涉及版权等问题,请作者在两周内速来电或来函联系。

中国教育在线

中国教育在线